| LATTENCY, DENSITY, INTERRUTT INTERVALI                         |                                              |

|----------------------------------------------------------------|----------------------------------------------|

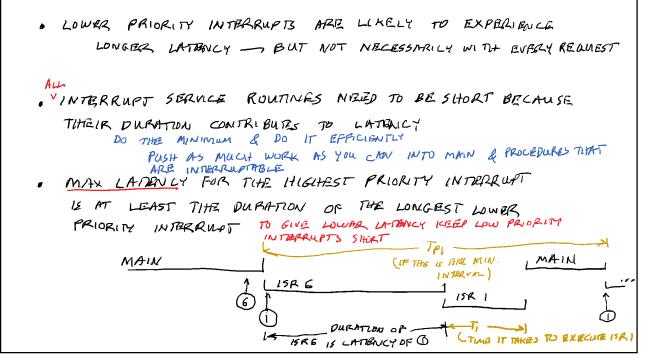

| THE WAY INTO PRAYTS MIGHT RUN<br>EACH TIC MARK IS & BOWDARY BE | MAACIHAVE<br>COPE<br>J<br>SWEEN INSTRUCTIONS |

| MAIN LATENCY FOR LATENCY FOR THE STANCE OF 6                   | Maig<br>L_c                                  |

| FROM TITE IRQ TO TITE<br>STARE OF EXECUTION OF<br>15R3         |                                              |

| LATERICY VARIES PROM<br>IRQ TO ERQ, EVEN FOR IRQ FOR 6         |                                              |

| CIRCLED NUMBERS ARE INTERRUPT REQUEST (IRG)                    | ()<br>ISR I HAD TO<br>ID BEFORE ERG I        |

|                                                                | HPPEN AGRIN                                  |

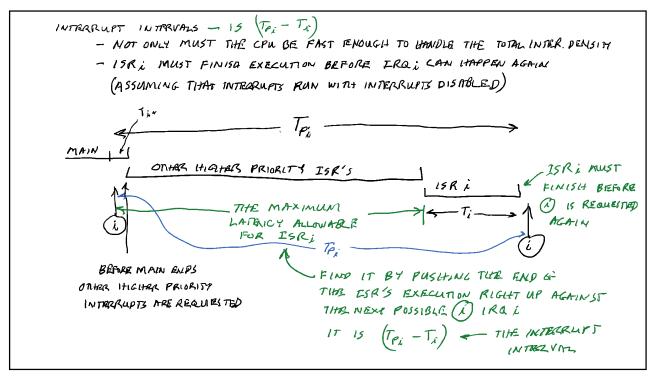

INTERRUPT DENSITY RATIO IS THE MAXIMUM FRACTION OR PERCENTAGE OF TIME THAT THE CPU COULD HAVE TO DEPICATE TO PROCESSING INTERRUPT SERVICE ROUTINES (ISR) IRQ -> HARDWARE SIGNAL 15 R - SOFTWARE THAC FOR EACH INTERRUPT i (1=1 15 HIGHEST PRIOR DOES THE WORK DEFINE T; = THE LONGEST POSSIBLE TIME IT WILL TAKE DESIGN CONKTRAINTS to EXECUTE THE ISR FOR INTERRUPT i NOT TYPICAL - HUMMANS MUST MARY 24 THE ODE TO FIGURE THIS OUT OF ACTUME TP: = THE SHORTEST POSSIBLE TIME WITHRUAL PERFIRMME BETWEEN REQUESTS FOR ISR & (A.K.A "PERIOD") EACH IN BERRUPT HAS AN ASSOCLATED DEALSING RATIO LOR; = "THE TOTAL EDR IS THE SUM SEDR: = STITES <100 - FOR RELIABILITY

MAKE SURE THAT THE INTERPORT INTERVELS (ONE FOR EACH i)

ARE NEVER EXCREPTED

DEFINE

$$N(i, x) = MARIMUM NUMBER OF THES INTR. x (HIGHER PRIORITY)

COULD BE REQUESTED PURING THE INTERPORT ANTERNAL FOR INTR. i

$N(i, x) = \begin{bmatrix} T_{P_i} - T_i \\ T_{P_i} \end{bmatrix}$

$N(i, x) = \begin{bmatrix} T_{P_i} - T_i \\ T_{P_i} \end{bmatrix}$

$N(x, x) = \begin{bmatrix} T_{P_i} - T_i \\ T_{P_i} \end{bmatrix}$

$RUMND UP TO INTECER

$\begin{bmatrix} 3.5c \\ 1 \end{bmatrix} = 4$

$\begin{bmatrix} 3.5c \\ 1 \end{bmatrix} = 4$

$\begin{bmatrix} 3.01 \\ 1 \end{bmatrix} \end{bmatrix}$

$AREQUESTS WILL (TUST) FIT$$$$

THE INTERRUPT IN TERVAL FOR EACH (i) CHECKING  $T_{i} + N(i, 1)T_{i} + N(i, 2)T_{2} + \dots + N(i, 2)T_{i} < T_{p_{i}} < T_{p_{i$ ALL THAS CAN CONTRIBUTE MUST NOT EXCRED TAS (ALTS INTERVAL LATENCRY FIRST ANALYZE CODE & DEFINE EACH TO MUD T: T. IS COMPUSTED FOR EACH INTR 2 15 LINGEST OF THE LONGEST MACHINE INSTRUCTION IN THE CODE OR THE LONGEST LOWER PRIDRITY INTERRUPT'S TI OR THE LONGEST CRITCAL REGION CAN PROVE N(i,n) = 1 $N(\dot{x}, \dot{x}) = \left(\frac{T_{P_{\dot{x}}} - T_{\dot{x}}}{T}\right)^{-2} ($  $\mathcal{N}(i,i) = i$

Interrupt example, Three interrupts (Interrupt 1 is highest priority) There are no critical regions, the longest instruction takes 1 ms to execute Interrupt sun with interrupts disabled For interrupt 3,  $T_{P_1} = 60$  ms,  $T_1 = 1.0$  ms,  $T_1 = 2.5$  ms, For interrupt 3,  $T_{P_2} = 20$  ms,  $T_2 = 2.5$  ms,  $T_{2+} = 1$  ms, For interrupt 3,  $T_{P_3} = 4$  ms,  $T_2 = 1.0$  ms,  $T_{3+} = 1$  ms, For interrupt 3,  $T_{P_3} = 4$  ms,  $T_2 = 1.0$  ms,  $T_{3+} = 1$  ms, For interrupt 3,  $T_{P_3} = 4$  ms,  $T_2 = 1.0$  ms,  $T_{1+} = 1.7$  ms, For interrupt 4,  $T_{P_3} = 4$  ms,  $T_{2+} = 1$  ms, For interrupt 4,  $T_{P_3} = 4$  ms,  $T_{2+} = 1$  ms, For interrupt 7,  $T_{2+} = 1$  ms, For interrupt 8,  $T_{P_3} = 4$  ms,  $T_{2+} = N(2, j)T_1 + N(2, j)T_1 + N(2, j)T_2 + \dots N(2, j)T_2 + \dots$